# CISC 7310X CO6d Intel 32- and 64-bit Architecture

Hui Chen

Department of Computer & Information Science

CUNY Brooklyn College

#### Acknowledgement

These slides are a revision of the slides provided by the authors of the textbook

#### Outline

• Example: The Intel 32 and 64-bit Architectures

• Example: ARMv8 Architecture

#### Example: The Intel 32 and 64bit Architectures

- Dominant industry chips

- Pentium CPUs are 32-bit and called IA-32 architecture

- Current Intel CPUs are 64-bit and called IA-64 architecture

- Many variations in the chips, cover the main ideas here

# Example: The Intel IA-32 Architecture

- Supports both segmentation and segmentation with paging

- Each segment can be 4 GB

- Up to 16 K segments per process

- Divided into two partitions

- First partition of up to 8 K segments are private to process (kept in local descriptor table (LDT))

- Second partition of up to 8K segments shared among all processes (kept in global descriptor table (GDT))

# Example: The Intel IA-32 Architecture (Cont.)

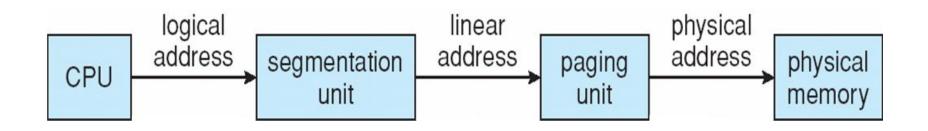

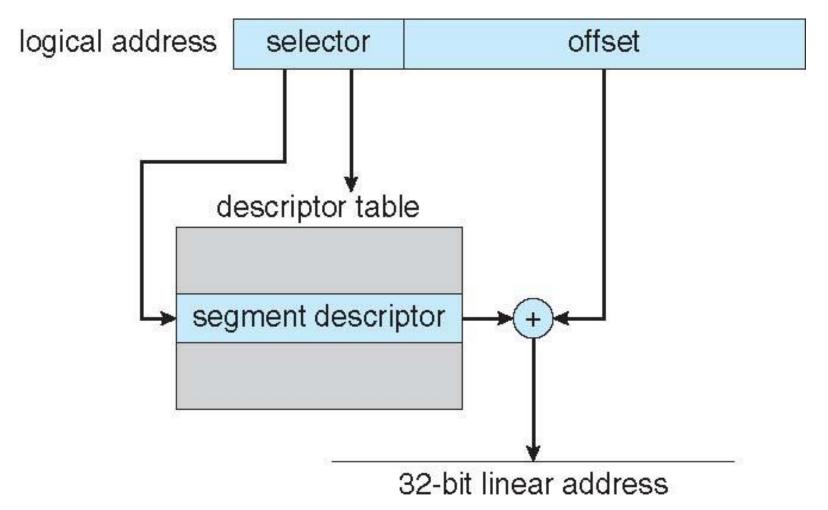

- CPU generates logical address

- Selector given to segmentation unit

- Which produces linear addresses

- Linear address given to paging unit

- Which generates physical address in main memory

- Paging units form equivalent of MMU

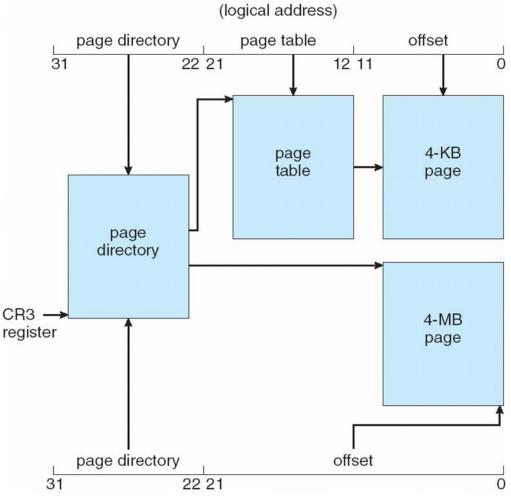

- Pages sizes can be 4 KB or 4 MB

## Logical to Physical Address Translation in IA-32

| page r | ıumber | page offset |  |  |  |

|--------|--------|-------------|--|--|--|

| $p_1$  | $p_2$  | d           |  |  |  |

| 10     | 10     | 12          |  |  |  |

#### Intel IA-32 Segmentation

# Intel IA-32 Paging Architecture

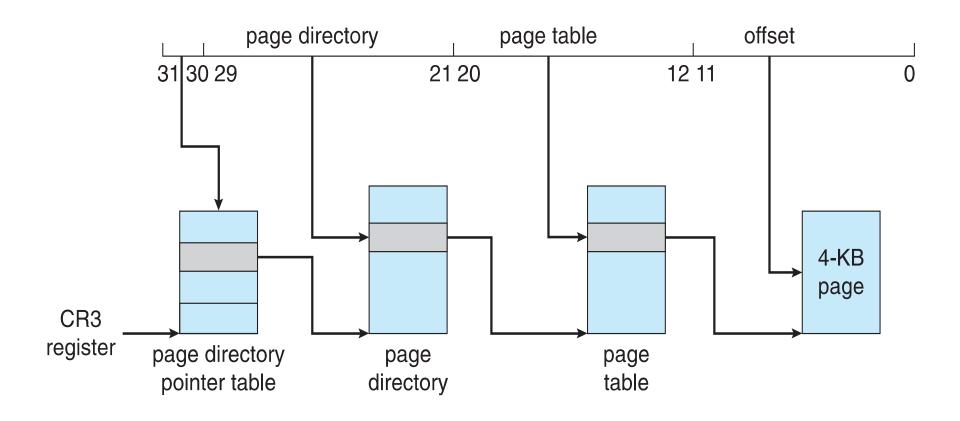

## Intel IA-32 Page Address Extensions

- 32-bit address limits led Intel to create page address extension (PAE), allowing 32-bit apps access to more than 4GB of memory space

- Paging went to a 3-level scheme

- Top two bits refer to a page directory pointer table

- Page-directory and page-table entries moved to 64bits in size

- Net effect is increasing address space to 36 bits -64GB of physical memory

#### Intel x86-64

- Current generation Intel x86 architecture

- 64 bits is ginormous (> 16 exabytes)

- In practice only implement 48 bit addressing

- Page sizes of 4 KB, 2 MB, 1 GB

- Four levels of paging hierarchy

- Can also use PAE so virtual addresses are 48 bits and physical addresses are 52 bits

|        |                | page map | )  | page dire | ectory            | page      |       | page  |      |        |   |

|--------|----------------|----------|----|-----------|-------------------|-----------|-------|-------|------|--------|---|

| unused | d <sub>I</sub> | level 4  |    | pointer t | able <sub> </sub> | directory |       | table |      | offset |   |

| 63     | 48 4           | .7       | 39 | 38        | 30 2              | 9         | 21 20 | 1     | 2 11 |        | 0 |

#### Questions?

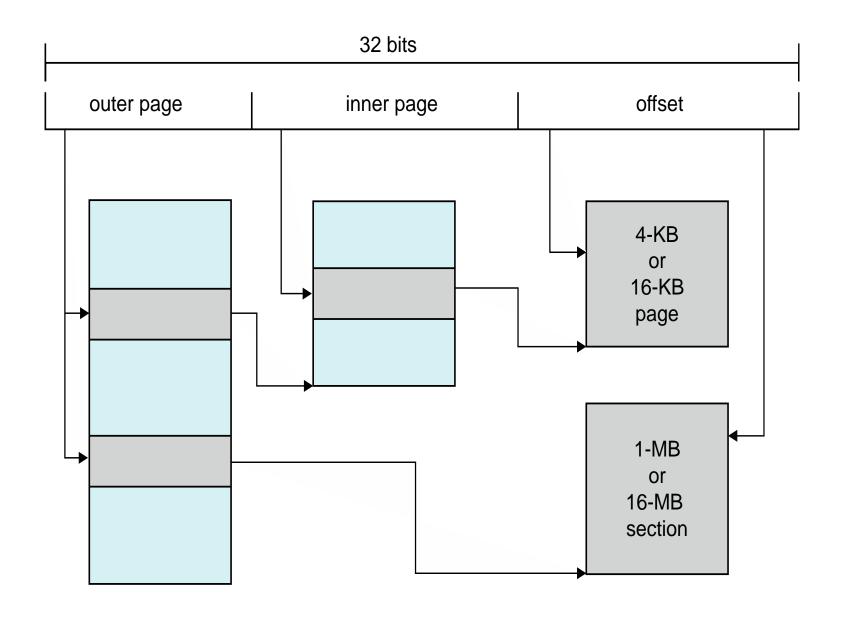

#### Example: ARM Architecture

- Dominant mobile platform chip (Apple iOS and Google Android devices for example)

- Modern, energy efficient, 32-bit CPU

- 4 KB and 16 KB pages

- 1 MB and 16 MB pages (termed sections)

- One-level paging for sections, two-level for smaller pages

- Two levels of TLBs

- Outer level has two micro TLBs (one data, one instruction)

- Inner is single main TLB

- First inner is checked, on miss outers are checked, and on miss page table walk performed by CPU

#### Questions?