#### CISC 3320 C18a Main Memory: Structure of Page Table

#### Hui Chen

Department of Computer & Information Science CUNY Brooklyn College

### Acknowledgement

These slides are a revision of the slides provided by the authors of the textbook via the publisher of the textbook

#### Outline

• Structure of the Page Table

- Swapping

- Example: The Intel 32 and 64-bit Architectures

- Example: ARMv8 Architecture

# Huge Page Table?

- Memory structures for paging can get huge using straight-forward methods

- Consider a 32-bit logical address space

- Page size of 4 KB (2<sup>12</sup>)

- Page table would have 1 million entries  $(2^{32} / 2^{12})$

- If each entry is 4 bytes → each process 4 MB of physical address space for the page table alone

- Don't want to allocate that contiguously in main memory

- How about a 64-bit logical address space?

## Structuring Page Table

- Hierarchical Paging

- Hashed Page Tables

- Inverted Page Tables

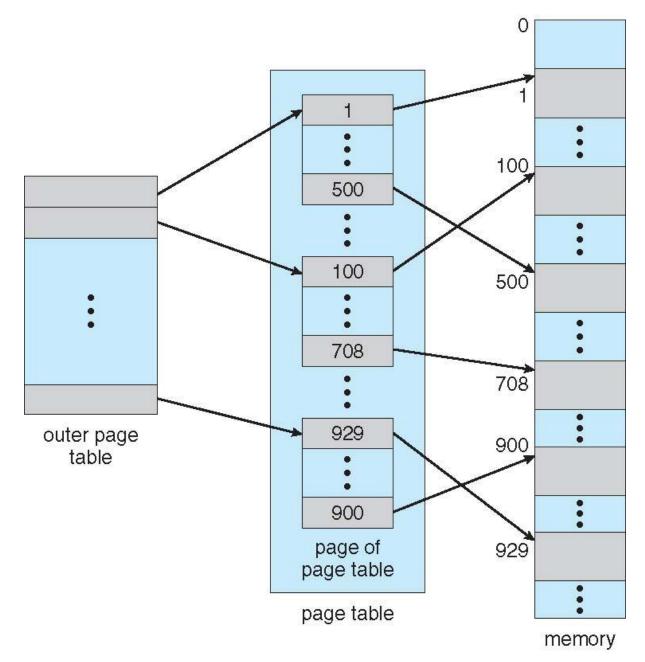

## Hierarchical Page Tables

- Break up the logical address space into multiple page tables

- A simple technique is a two-level page table

- We then page the page table

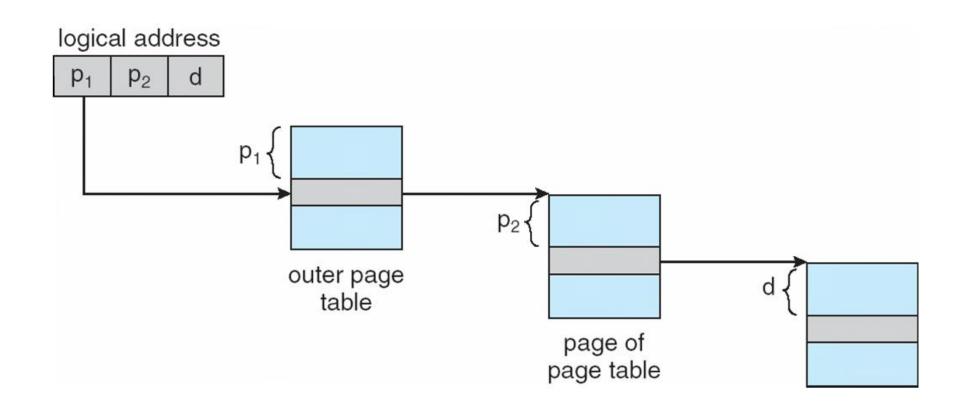

# Two-Level Paging: Example

- A logical address (on 32-bit machine with 1K page size) is divided into:

- a page number consisting of 22 bits

- a page offset consisting of 10 bits

- Since the page table is paged, the page number is further divided into:

- a 10-bit page number

- a 12-bit page offset

- Thus, a logical address is as follows: page number page offset  $p_1$   $p_2$  d 10 10 12

- where  $p_1$  is an index into the outer page table, and  $p_2$  is the displacement within the page of the inner page table

- Known as forward-mapped page table

#### Address-Translation Scheme

## 64-bit Logical Address Space

- Even two-level paging scheme not sufficient

- If page size is 4 KB (2<sup>12</sup>)

- Then page table has 2<sup>52</sup> entries

- If two level scheme, inner page tables could be 2<sup>10</sup> 4-byte entries

- Address would look like

| outer page | inner page | offset |  |

|------------|------------|--------|--|

| $p_1$      | $p_2$      | d      |  |

| 42         | 10         | 12     |  |

- Outer page table has 2<sup>42</sup> entries or 2<sup>44</sup> bytes

- One solution is to add a 2<sup>nd</sup> outer page table

- But in the following example the 2<sup>nd</sup> outer page table is still 2<sup>34</sup> bytes in size

- And possibly 4 memory access to get to one physical memory location

# Three-Level Paging Scheme

| outer page | inner page | offset |  |  |

|------------|------------|--------|--|--|

| $p_1$      | $p_2$      | d      |  |  |

| 42         | 10         | 12     |  |  |

| 2nd outer page | outer page | inner page            | offset |

|----------------|------------|-----------------------|--------|

| $p_1$          | $p_2$      | <i>p</i> <sub>3</sub> | d      |

| 32             | 10         | 10                    | 12     |

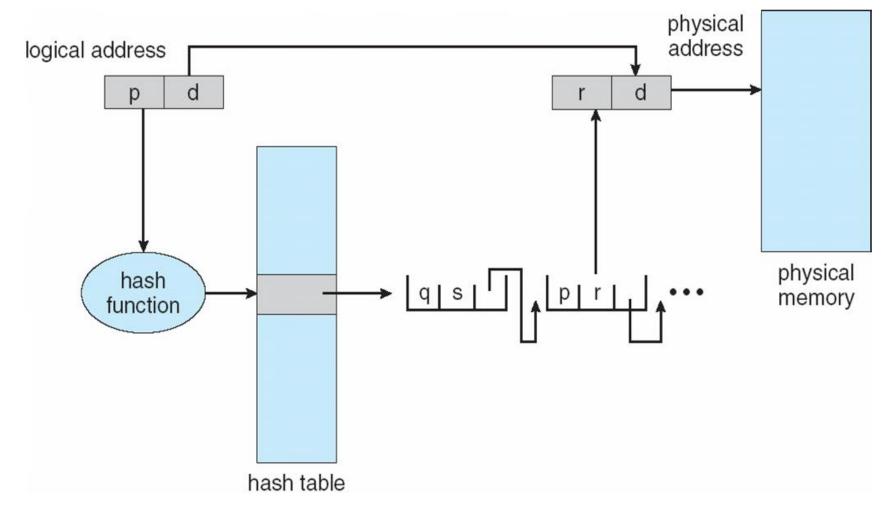

# Hashed Page Tables

- Common in address spaces > 32 bits

- The virtual page number is hashed into a page table

- This page table contains a chain of elements hashing to the same location

- Each element contains (1) the virtual page number (2) the value of the mapped page frame (3) a pointer to the next element

- Virtual page numbers are compared in this chain searching for a match

- If a match is found, the corresponding physical frame is extracted

- Variation for 64-bit addresses is clustered page tables

- Similar to hashed but each entry refers to several pages (such as 16) rather than 1

- Especially useful for sparse address spaces (where memory references are non-contiguous and scattered)

# Hashed Page Table

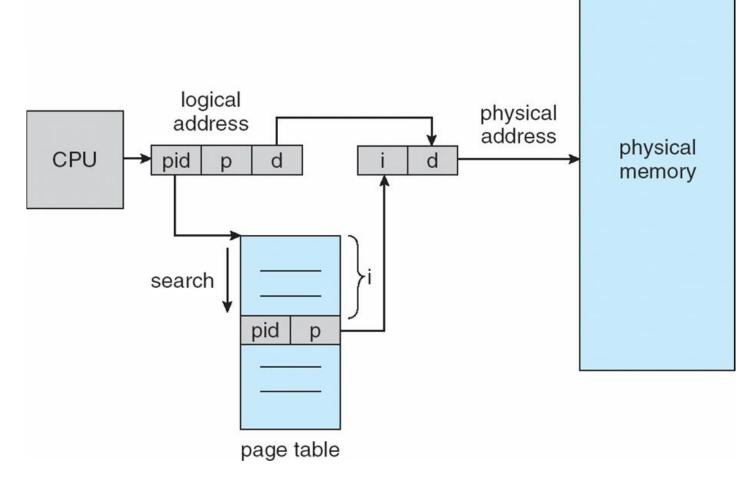

# Inverted Page Table

- Rather than each process having a page table and keeping track of all possible logical pages, track all physical pages

- One entry for each real page of memory

- Entry consists of the virtual address of the page stored in that real memory location, with information about the process that owns that page

- Decreases memory needed to store each page table, but increases time needed to search the table when a page reference occurs

- Use hash table to limit the search to one or at most a few pagetable entries

- TLB can accelerate access

- But how to implement shared memory?

- One mapping of a virtual address to the shared physical address

#### Inverted Page Table Architecture

#### Oracle SPARC Solaris

- Consider modern, 64-bit operating system example with tightly integrated HW

- Goals are efficiency, low overhead

- Based on hashing, but more complex

- Two hash tables

- One kernel and one for all user processes

- Each maps memory addresses from virtual to physical memory

- Each entry represents a contiguous area of mapped virtual memory,

- More efficient than having a separate hash-table entry for each page

- Each entry has base address and span (indicating the number of pages the entry represents)

#### Oracle SPARC Solaris

- TLB holds translation table entries (TTEs) for fast hardware lookups

- A cache of TTEs reside in a translation storage buffer (TSB)

- Includes an entry per recently accessed page

- Virtual address reference causes TLB search

- If miss, hardware walks the in-memory TSB looking for the TTE corresponding to the address

- If match found, the CPU copies the TSB entry into the TLB and translation completes

- If no match found, kernel interrupted to search the hash table

- The kernel then creates a TTE from the appropriate hash table and stores it in the TSB, Interrupt handler returns control to the MMU, which completes the address translation.

#### Questions?

- Page table too large?

- Hierarchical Paging

- Hashed Page Tables

- Inverted Page Tables